# Design of a Portable Fast Scan Cyclic Voltammetry Device Utilizing Pulse Width Modulation for Waveform Generation

Nora Szymkowski

A Thesis Submitted to the Graduate Faculty of

# GRAND VALLEY STATE UNIVERSITY

In

Partial Fulfillment of the Requirements

For the Degree of

Master of Science

School of Engineering

August 2024

**Thesis Approval Form**

The signatories of the committee below indicate that they have read and approved the thesis of Nora Cole in partial fulfillment of the requirements for the degree of Master of Electrical and Computer Engineering.

| M - 1/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Brun Grung,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7/10/24 |

| Dr. Brian Krug, Thesis committee chair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Date    |

| Naberd KondelaFt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |

| • Manufactor Income Control | 7/10/24 |

| Dr. Nabeeh Kandalaft, Committee member                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Date    |

| $\langle \langle \rangle \rangle$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7/10/24 |

| Dr. Eric Ramsson, Committee member                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Date    |

Accepted and approved on behalf of the Padnos College of Engineering

Dean of the College

Accepted and approved on behalf of the Graduate Faculty

Deal of The Graduate School

8/5/2024

Date

7/25/2024

Date

#### Abstract

Fast Scan Cyclic Voltammetry (FSCV) is a widely used electrochemical technique for real-time measurement of the brain's chemical messengers, including the molecule dopamine, with high temporal resolution. Currently the financial burden of performing FSCV is quite high, ranging from \$8,000 to \$20,000+ making the barrier to entry nearly insurmountable for laboratories and classrooms at small institutions. The purpose of this project was to develop a Do-It-Yourself (DIY), portable, and cost-effective FSCV system for use in laboratory and classroom settings. The project aimed to create a compact and cost-effective system that could be used by researchers and educators to study dopamine levels and dynamics in various settings. By utilizing a Hercules Launchpad by Texas Instruments, a device was designed to perform FSCV of dopamine. The device was able to successfully produce the required waveform and collect the results. This project offers proof of concept for the use of Pulse Width Modulation (PWM) in the generation of a FSCV triangle waveform for dopamine concentration measurements.

| Table of | Contents |

|----------|----------|

|----------|----------|

| Title Page                                                                                                            | 1                    |

|-----------------------------------------------------------------------------------------------------------------------|----------------------|

| Approval Page                                                                                                         | 2                    |

| Abstract                                                                                                              | 3                    |

| Table of Contents                                                                                                     | 4                    |

| List of Tables                                                                                                        | 5                    |

| List of Figures                                                                                                       | 6                    |

| List of Equations                                                                                                     | 7                    |

| Chapter 1 Introduction<br>Introduction<br>Purpose                                                                     | 8<br>8<br>9          |

| Chapter 2 Review of Literature                                                                                        | 12                   |

| Chapter 3 Methodology<br>Hardware<br>Software                                                                         | 21<br>21<br>24       |

| Chapter 4 Results                                                                                                     | 31                   |

| Chapter 5 Discussion and Conclusions.<br>Discussions.<br>Conclusions.<br>Future Work.                                 | 35<br>35<br>37<br>37 |

| Appendices.<br>Appendix I – Schematic.<br>Appendix II – Hercules Microcontroller Code.<br>Appendix III – Data Sheets. | 38<br>38<br>39<br>49 |

| References                                                                                                            | 189                  |

# List of Tables

| Table 1. Project Bill of Materials        | 33 |

|-------------------------------------------|----|

| Table 2. Component Only Bill of Materials | 34 |

# List of Figures

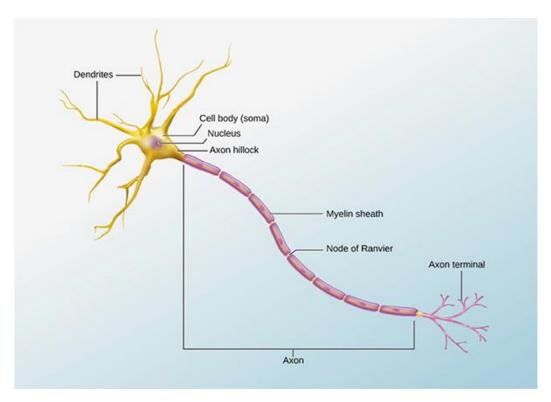

| Figure 1. Neuron Diagram                                                      | 12 |

|-------------------------------------------------------------------------------|----|

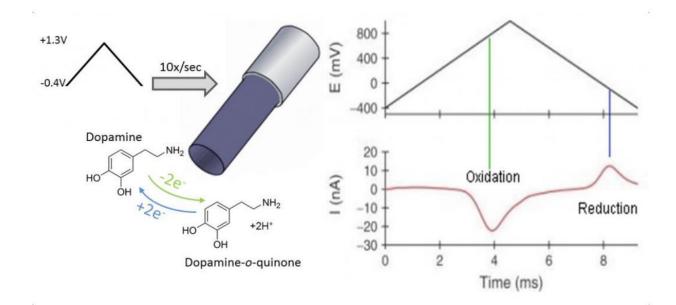

| Figure 2. Waveform and Oxidation-Reduction Reactions                          | 19 |

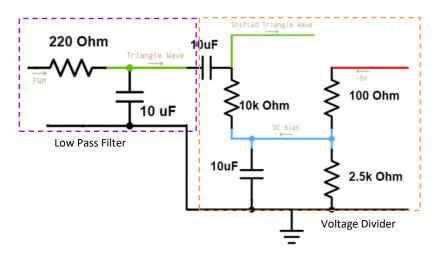

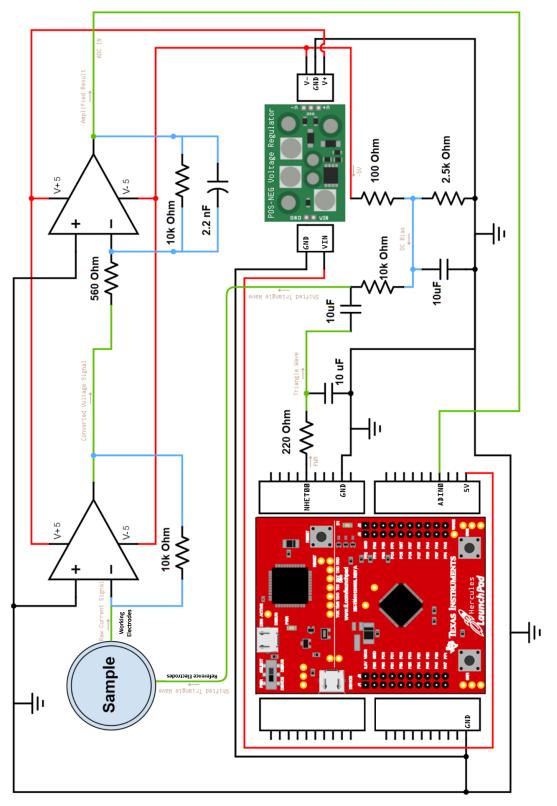

| Figure 3. Waveform Generation Signal Conditioning Circuit                     | 22 |

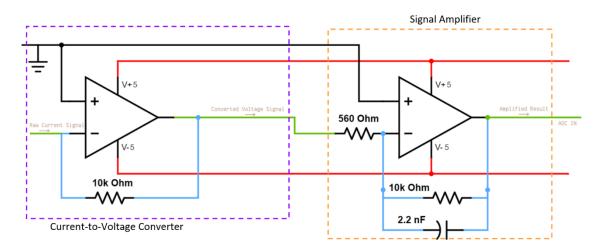

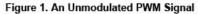

| Figure 4. Current-to-Voltage Converter and Amplifier Circuit                  | 23 |

| Figure 5. Block Diagram for PWM Triangle Wave Generation Code                 | 25 |

| Figure 6. Main Function Code for ADC and SCI Modules                          | 29 |

| Figure 7. Block Diagram for Data Processing Python Script                     | 30 |

| Figure 8. Oscilloscope Measurements of Triangle Wave Generation               | 31 |

| Figure 9. Current Waveform Outputs for Dummy Cell, Hercules vs. Gold Standard | 32 |

# List of Equations

| Equation 1. Voltage Divider Equation        | 23 |

|---------------------------------------------|----|

| Equation 2. Current Follower Equation       | 24 |

| Equation 3. Amplifier Gain Equation         | 24 |

| Equation 4. Loop Resolution Period Equation | 27 |

#### **Chapter 1 Introduction**

# Introduction

The field of neuroscience and research into chemical signaling in the brain is of great importance for several reasons including: understanding brain function, studying neurological disorders and mental health conditions, designing new treatments for those disorders and conditions, and developing new technology [1].

Neuroscience research aims to uncover the complex workings of the brain, including how it processes information, controls behavior, and regulates various bodily functions. By studying chemical signaling, researchers can gain insights into the fundamental mechanisms underlying brain function, such as learning, memory, emotions, decision-making, and sensory processing [2]. Their research also helps shed light on the causes, mechanisms, and potential treatments for neurological disorders and mental health conditions. Chemical signaling abnormalities, such as imbalances in neurotransmitters are often implicated in conditions like Parkinson's disease, Alzheimer's disease, depression, anxiety disorders, and schizophrenia [1]. Understanding the chemical signaling disruptions associated with these conditions can aid in the development of targeted interventions and therapies.

Investigating chemical signaling in the brain provides critical insights for drug discovery and development. Many drugs act on specific receptors or modulate neurotransmitter levels to treat neurological and psychiatric disorders. Research into chemical signaling pathways helps identify potential drug targets and aids in the development of more effective and specific pharmacological interventions. Additionally, advancements in understanding chemical signaling contribute to the development of brain-computer interfaces (BCIs). BCIs enable direct communication between the brain and external devices, offering potential solutions for individuals with paralysis or sensory impairments. Research in chemical signaling assists in designing interfaces that can interpret and modulate neuronal activity, facilitating bidirectional communication between the brain and external devices [3].

Fast Scan Cyclic Voltammetry (FSCV) is a widely used electrochemical technique for real-time measurement of the brain's chemical messengers, including the molecule dopamine, with high temporal resolution. FSCV involves applying a voltage waveform to a carbon-fiber electrode and measuring the resulting electrical currents as the molecules undergo oxidation or reduction reactions [4].

Currently the financial burden of performing FSCV is quite high, ranging from \$8,000 to \$20,000+. This makes the barrier to entry nearly insurmountable for laboratories and classrooms at small institutions. A low cost, portable FSCV device would make classroom demonstrations and proof of concept research for grant proposals possible in these more resource-restricted environments.

#### Purpose

The purpose of this project was to develop a DIY, portable, and cost-effective FSCV system for use in laboratory and classroom settings. The project aimed to create a compact and cost-effective system that could be used by researchers and educators to study dopamine levels and dynamics in various settings, including resource-constrained environments such as small university laboratories and classrooms. The project sought to achieve the following objectives:

Affordability and Accessibility: The focus of the project was on utilizing low-cost components and creating easily implementable, open-source software to develop a 'DIY' FSCV device that is affordable and accessible to a wide range of users. By reducing the production cost, the project aimed to remove financial barriers and promote widespread access to FSCV technology.

- 2. Portability and Compact Design: The device was designed to be portable and lightweight, allowing for easy transportation and use in different settings. Its compact form factor was intended to enable researchers and educators to conduct experiments and demonstrations outside the confines of a traditional laboratory.

- 3. Real-Time Data Acquisition and Analysis: The device incorporated hardware and software designed to enable real-time data acquisition, analysis, and visualization of dopamine levels. In order to accomplish this the device was required to perform the following tasks:

- a. Generation of the stimulus waveform: The present device was designed with the ability to produce just one triangle waveform. The waveform selected is a very commonly used one when measuring dopamine concentrations.

- b. Measurement of the current flow in the electrode: The device was designed with the intention to be compatible with a single carbon fiber 'working' electrode and a single carbon fiber 'reference' electrode.

- c. Amplification of the recorded current waveform: Due to the miniscule nature of the current waveform produced, the device required circuitry to amplify this waveform to make it interpretable.

- d. Conversion of the current waveform to a digital signal: In order for the data to be retrieved by the device, the analog signal would have to be converted into a digital one.

- e. Communication of the digital signal to a PC: Once the signal had been converted to be digital, it was then required to be sent to a PC for analysis.

- f. Analysis and display of the resulting current signal: The final signal would then have to be interpreted by an algorithm and displayed in order for it to be useful to researchers.

- 4. Versatility and Compatibility: The open-source, 'DIY' nature of the FSCV device was intended to allow for future users and developers to build on the current work. With further development, future iterations of the device could be made compatible with a variety of electrode configurations and be made capable of producing multiple waveforms in order to support the measurement of different neurotransmitters, such as serotonin and glutamate.

- 5. Educational and Research Applications: The project aimed to foster educational and research opportunities by providing an affordable tool for studying neurotransmitter dynamics. The device will empower students, educators, and researchers to explore the principles of neuroscience promoting scientific discovery and understanding.

The final objective of this project was to attempt to address the limitations in the portable FSCV system developed by Foster at Grand Valley State University. The intent was to consolidate the system to just one microcontroller capable of performing both the waveform generation and data acquisition simultaneously. It was also a goal to, if possible, ensure the system performs well thermally at ambient temperatures without the need for makeshift cooling methods.

## **Chapter 2 Review of Literature**

## **Mechanism of Neurotransmitters**

The human body uses its nervous system to think, move, feel, see, hear, speak, taste, and smell. The brain, spinal cord, and a network of peripheral neurons make up the nervous system and are able to communicate and process massive amounts of sensory data, control the voluntary muscular system, ensure life supporting organ functions work seamlessly, store memories, think critically, and much more [2]. It is able to accomplish all of this simultaneously and at incredible speeds. Much of this nervous tissue is constructed of a powerful cell type called neurons [1]. A neuron and its basic anatomy are shown below in Figure 1.

Figure 1. Neuron Diagram [5]

Neurons are similar to other cell types in that they have a cell body which contains a nucleus responsible for the cell's maintenance; however, they have other highly specialized structures which allow them to participate in the momentous task of operating the human body.

These structures include the dendrites (long tendrils protruding from the cell body), the axon (the long cable like structure that makes up much of the cell), the axon hillock (the junction where the cell body meets the axon), and the axon terminal (the branched end of the axon) [2]. Each of these structures is identified above in Figure 1.

Neurons transmit data to, from, and throughout the brain via electrical impulses that propagate along the length of each cell. When the dendrites of a cell are stimulated, ion channels are opened which create a local change in the potential difference across the cell membrane. This impulse, known as a graded potential, travels through the cell body toward the axon. When a great enough graded potential arrives at the axon hillock, a strong impulse known as an action potential is triggered and travels down the length of the axon to the axon terminal. This terminal end does not physically connect to the following neurons, so in order for the signal to pass from one neuron to the next, the signal must be converted into a chemical one. Specialized molecules called neurotransmitters are released from the axon terminal into the extracellular space between cells known as the synapse. These molecules bind to receptors on the dendrites of the postsynaptic neuron, stimulating another graded potential and thus the signal continues. Once the signal has been successfully passed, the neurotransmitter molecules are taken back up by the presynaptic neuron. This allows the synapse and the postsynaptic receptors to be cleared so that a future signal can be transmitted. [1].

There are many dozens of neurotransmitters that have been identified in the human body to date. Some function as excitatory, meaning they aid in triggering further action potentials as discussed above, and others as inhibitory, meaning they work to stop or reduce further action potentials, and still others can do both of these depending on the specific circumstances [1]. Both are critical to keeping all functions of the body working properly and in balance. Although there are many neurotransmitters present and working in the nervous system, there are just several key ones which do much of the work and are specialized to regulate and govern certain functions within the brain and body. Some of these molecules are Glutamate, Gamma-Aminobutyric Acid (GABA), Epinephrine, Norepinephrine, Histamine, Serotonin, Oxytocin, Acetylcholine, and Dopamine [2]. For the purposes of this project, the focus will be on dopamine.

## Dopamine

The importance of the role of the dopamine molecule in the human body cannot be overstated. Considered both a neurotransmitter and a hormone, dopamine plays a vital role in many bodily functions [1]. To name a few: movement, attention, motivation/reward, learning, and mood [2]. Additionally, the dopamine molecule functions as a precursor to epinephrine and norepinephrine [6], two pivotal neurotransmitters/hormones in the human body responsible for producing the critical "fight-or-flight" response to perceived danger [2].

One of the first known roles of dopamine was its impact on coordination and smooth movement [7]; however, in recent years, the findings suggest that one of the primary roles of dopamine is governing motivation and reward [8]. It is thought that the release of this molecule is necessary for the initiation of an action as well as the reinforcement of that action [9]. If the outcome of an action is as expected, the dopamine release in response to the outcome reflects that. Likewise, if the outcome is either better or worse than expected, the dopamine release increases or decreases correspondingly to either positively or negatively reinforce that action [10].

It is also hypothesized that the release of dopamine in the hippocampus in response to a novel event induces long term memory storage [11], and that dopamine plays a role in memory deletion as well [12]. In this way, dopamine has a massive impact on how the human brain learns

from actions and experiences. It is well known that drugs like amphetamines form dependencies because they act directly on dopamine terminals, but it is now also suggested that any substance that triggers dopamine's reward system can become habit forming including things like cannabis and caffeine [13]. All of these roles of dopamine reveal just how important it is when it comes to human behavior at large. There is still plenty that neuroscientists do not understand when it comes to dopamine and its functions, and it is an ongoing area of research to understand how to manipulate and maintain proper dopamine function.

#### **Measurement Techniques**

Over the years of research into neurotransmitters and more specifically dopamine, many techniques have been developed and used to measure dopamine levels in the brains of animals and humans. Some of these methods include:

- 1. Mircodialysis: This method of neurotransmitter measurement is invasive and is most commonly used in animal models. This method involves inserting a semipermeable membrane on the end of a probe into a particular brain region through which a sample of the extracellular fluid can be collected and then analyzed [14]. While not considered the preferred method, this technique has been historically used to measure dopamine concentrations in the interstitial space of a brain structure or region [15].

- 2. Positron Emission Tomography (PET): This method utilizes a PET scan and is therefore considered a non-invasive measurement technique. This procedure, "enables the direct measurement of components of the dopamine system in the living human brain. It relies on radiotracers which label dopamine receptors, dopamine transporters, precursors of dopamine or compounds which have specificity for the enzymes which

degrade dopamine," [16], all of which give researchers an abundance of information about the dopamine system at large.

- 3. Functional Magnetic Resonance Imaging (fMRI): This method employs an MRI which has the advantages of being non-invasive as well as non-radiological. However, it is more limited than its more invasive counterparts in that it cannot directly measure dopamine levels. This technique instead utilizes proxy measures that can then be extrapolated to a high-level understanding of "long term dopamine function or degeneration of dopaminergic neurons", [17].

- 4. Single-Cell Recordings: This method, while more cutting edge, is considered invasive and highly technical. This technique involves the insertion of very fine microelectrodes directly into individual neurons in order measure changes in voltage and current. This allows single cells to be monitored for activity in response to various external stimuli [18]. This makes single cell recordings highly detailed and granular, but also cost-prohibitive as well as technically prohibitive.

- 5. Fast Scan Cyclic Voltammetry (FSCV): This invasive method can measure dopamine concentrations with a high level of sensitivity in real time. This technique involves the placement of two single carbon-fiber electrodes into a brain sample or brain region. Changes in the electrical current as dopamine is oxidized and then reduced can be measured and then used to determine the concentration of dopamine present in the sample with great accuracy and temporal resolution [4]. It is noteworthy that this method is also quite cost-prohibitive.

While not comprehensive, this list represents some of the most common measurement techniques for neurotransmitters and for dopamine specifically. When to employ a given technique can only be decided based on the requirements of the experiment in light of the strengths and weaknesses of each method. For the purposes of this project, the focus will be on FSCV.

#### **FSCV Overview**

Since only discussed very briefly above, this section will be used to delve deeper into the measurement technique known as Fast Scan Cyclic Voltammetry or FSCV. As mentioned previously, this method involves the placement of two single carbon-fiber electrodes into a brain sample or region; one is known as the working electrode and the other is known as the reference electrode. These electrodes are then used both to incite an oxidation-reduction reaction of dopamine and to measure the changes in the electrical current that result from that reaction. Systems that perform these tasks typically need the following components:

- Electrode: A thin carbon fiber around 5-30 µm in diameter that is usually insulated aside from the very end which is placed into the solution or sample. These electrodes are highly conductive in order to be sensitive enough for neurotransmitter detection.

- Potentiostat: An electronic device that is used to apply the correct voltage waveform to the working electrode and to measure and amplify the very small electrical currents produced by the experiment.

- 3. Data Acquisition System: Equipment used to capture and record the measurements from FSCV using an analog-to-digital converter (ADC). This takes the true analog measurements and digitizes them so they can be processed and stored by a computer.

- 4. Control and Analysis Software: Specialized software to control the initiation, recording, and visualization of incoming data in real time. May also include additional tools and algorithms for data analysis and neurotransmitter quantification.

17

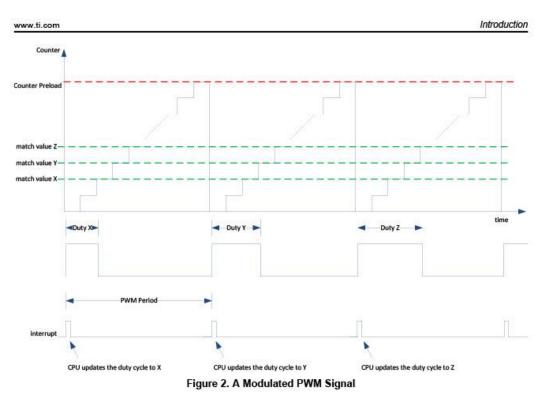

The most common waveform used for FSCV of dopamine is a triangular waveform. The triangular waveform is simple, effective, and widely employed due to its favorable characteristics for dopamine oxidation and reduction measurements. The specific voltage parameters associated with the triangular waveform include: the initial potential (the starting voltage of the triangular waveform commonly set to a slightly negative potential such as -0.4V to establish a baseline and prepare for the oxidation phase of dopamine), the peak potential (the highest voltage reached during the positive phase of the triangular waveform, commonly 1.3V), the final potential (the voltage at the end of the negative phase of the triangular waveform, typically the same value as the initial potential), and the scan rate (the speed at which the triangular waveform is scanned, for instance, 400V/s).

This waveform is typically repeated 10 times per second for the duration of the measurement. During the positive phase of the triangular waveform, the voltage applied to the carbon-fiber electrode increases. As the voltage exceeds around 0.6V, dopamine molecules near the electrode undergo oxidation to form dopamine-*o*-quinone. During this reaction dopamine loses 2 electrons which incites a measurable electrical current at the electrode. This electrical current is directly proportional to the rate of dopamine oxidation, which can then be extrapolated to calculate the concentration of dopamine in the electrodes immediate proximity. During the negative phase of the triangular waveform, the voltage applied to the electrode decreases. At around -0.1V, the reduction of dopamine-*o*-quinone occurs and the molecule gains 2 electrons to once again become dopamine. The reduction reaction also generates an electrical current, which is proportional to the rate of dopamine reduction and, hence, the concentration of dopamine-*o*-quinone near the electrode.

The electrical currents generated during both the oxidation and reduction reactions are measured by the FSCV setup which amplifies and records these currents as a function of the applied voltage. By analyzing the recorded current data, researchers can determine how dopamine concentration changes over time. An image of the waveform as well as the chemical reactions and the resulting current measurements can be seen in Figure 2.

Figure 2. Waveform and Oxidation-Reduction Reactions [19]

#### **Existing Devices and Previous Work**

Devices such as the WaveNeuro Potentiostat by Pine Research are typically used to perform FSCV. National Instruments data acquisition cards as well as their LABVIEW® software are also required to perform the experiment. The cost of all of this equipment can range from around \$8000 on the low end for simple setups all the way up to \$20000+ for more complex setups. With this sort of price tag, FSCV is incredibly cost-prohibitive for smaller institutions, researchers, and educators who wish to demonstrate and utilize the effectiveness of FSCV for the measurement of dopamine. This reveals an opportunity to provide a lower cost option.

The effort to lower the financial burden of this measurement technique is not novel. Previous work in this area was completed by Jayson Foster of Grand Valley State University in which he designed an Arduino based system to perform the waveform generation and data acquisition and utilized MATLAB to analyze the data and display the result. In the course of that project, it was determined that the microcontroller was unable to simultaneously perform the signal generation for the triangle waveform and the data collection through the ADC. In order to combat this, the tasks of waveform generation and data acquisition were divided between two separate microcontrollers. Additionally, it was discovered that the thermal load resulting in the system was producing inaccurate data and makeshift cooling methods were required to perform the measurements.

# **Chapter 3 Methodology**

The development of the device was broken down into two distinct areas: hardware and software. Tasks categorized under the hardware category included: researching and selecting a microcontroller and designing the circuit for the waveform signal conditioning and result signal amplification. Tasks categorized under the software category included: writing the firmware for the microcontroller to perform the waveform generation and data collection (written in C) and writing the script for the data analysis and display (written in python).

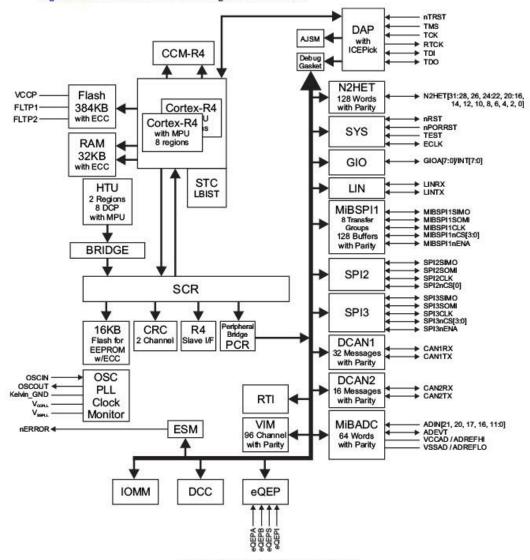

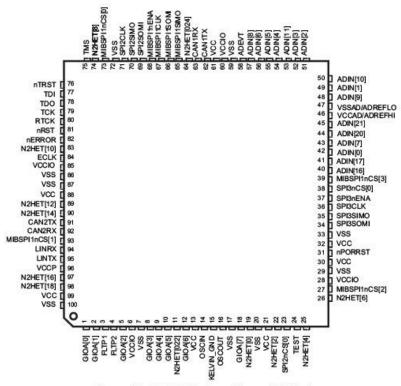

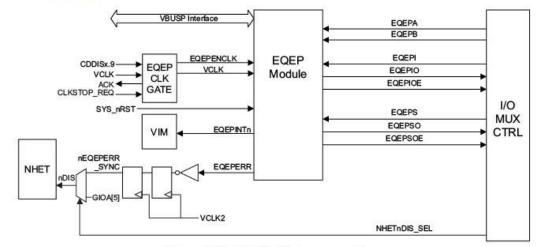

#### Hardware

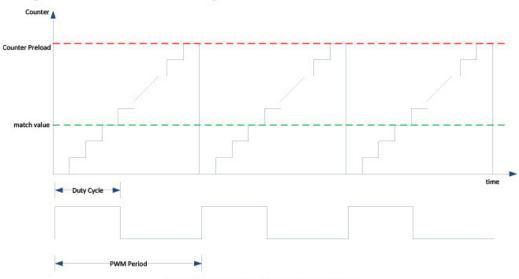

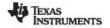

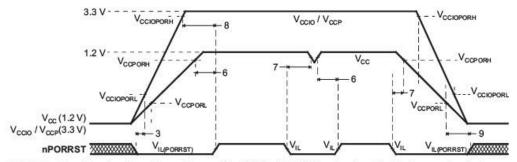

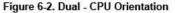

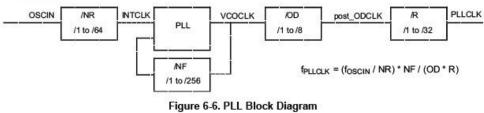

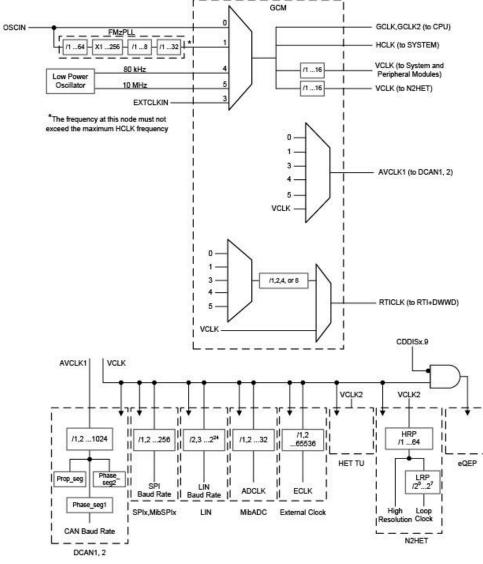

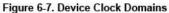

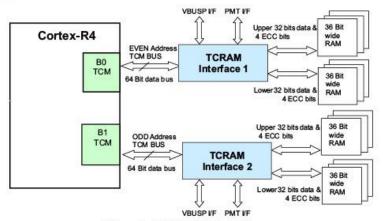

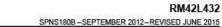

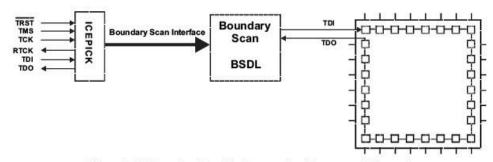

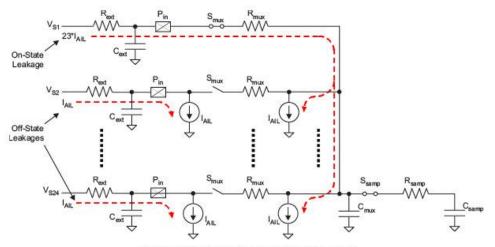

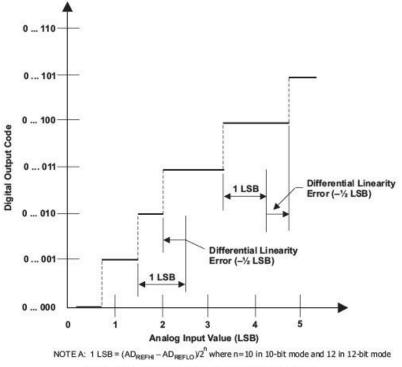

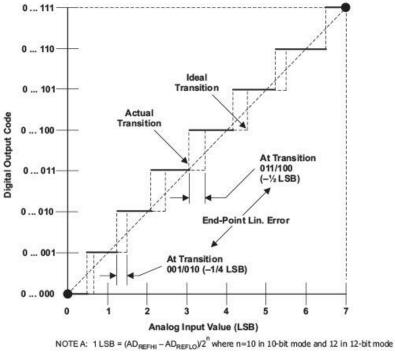

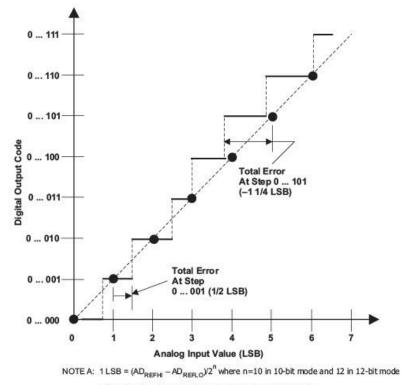

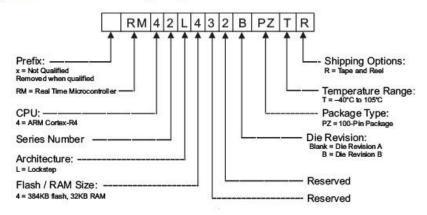

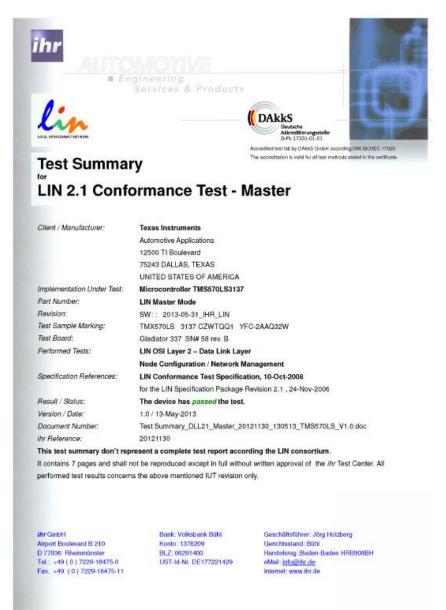

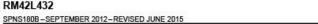

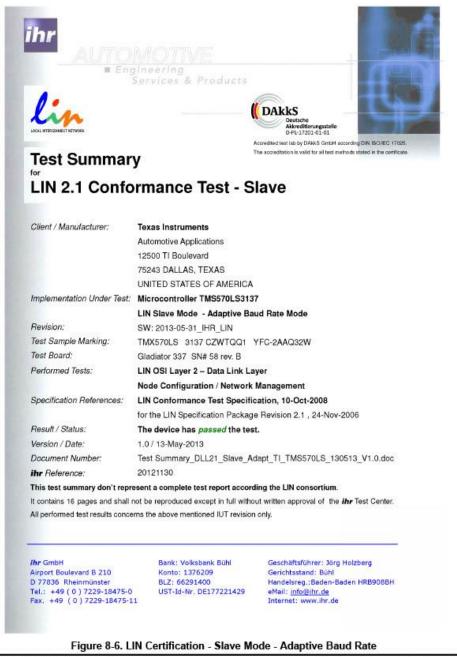

The board chosen for this project was the Hercules RM42x LaunchPad, a development kit offered by Texas Instruments (TI) specifically designed for the Hercules RM42x series of microcontrollers. The Hercules line of microcontrollers is designed for safety-critical designs and as such is commonly used in biomedical applications. The Hercules microcontrollers often include specialized peripherals and modules to support real-time operations making them a good option for this application. The launchpad utilizes the Hercules 100-pin RM42L432 microcontroller. Key specs for this launchpad that are most relevant to this project are a 12-bit analog to digital converter (ADC), and a programmable high-end timer (HET) module designed for highly accurate real-time operations. The HET module is capable of using Pulse Width Modulation (PWM) to generate complex waveforms independently of the main CPU. This makes it an ideal solution for the current project in that all of the signal generation can be done separately from the data acquisition, ensuring the two processes do not conflict without the need for a second microcontroller.

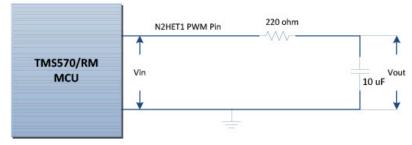

PWM is a method of encoding a voltage onto a fixed frequency carrier wave. The frequency of the PWM will be fixed while the duty cycle will vary between 0% and 100%. The

21

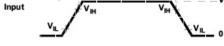

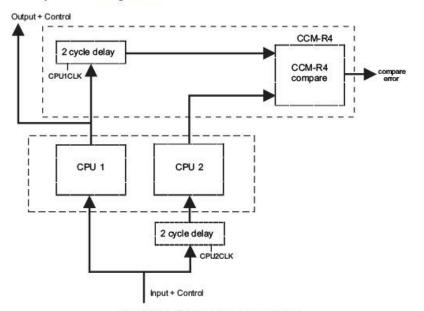

percentage of the on-time will be proportional to the output signal voltage. For example, a 0% duty cycle produces a 0 V output while a 100% duty cycle produces a peak-to-peak voltage Vp-p equal to the Vccio, which is the I/O power supply voltage to the microcontroller. The nominal Vccio is 3.3 V in Hercules microcontrollers so a 50% duty cycle would have produced an output voltage equal to 1.65 V. The PWM method is a low-cost way of implementing a digital-to-analog converter (DAC). By time-varying the duty cycle percentage, it is possible to generate an arbitrary analog waveform. The output signal needed to go through a simple analog low-pass filter to remove the high frequency components. This filter is constructed from a 220 $\Omega$  resistor and a 10 $\mu$ F capacitor, which can be seen in Figure 3. The full schematic for the project can be found in Appendix I. The filtered signal was the expected triangle shape; however, it is also noteworthy that the microcontroller is only capable of producing signals between 0V and 3.3V. As discussed previously, the parameters for the present triangle wave require the signal to range from -0.4V to 1.3 V. The purpose of the remainder of the circuit shown in Figure 3 is to shift the triangle wave signal down to the required level utilizing a voltage divider.

Figure 3. Waveform Generation Signal Conditioning Circuit

The first strategy to shift the signal down was simply to run the signal through a  $10\mu$ F capacitor since this would essentially equalize the amount of signal that exists above and below 0V. It was

determined that this strategy did not shift the signal enough to satisfy the requirements, so a voltage divider was utilized to further bias the signal down by almost 0.2V. Equation 1 was used to design the voltage divider circuit.

$$V_{out} = V_{in} \frac{R_2}{R_1 + R_2} \tag{1}$$

Where  $V_{out}$  is the output voltage,  $V_{in}$  is the input voltage,  $R_1$  is the voltage side resistor, and  $R_2$  is the ground side resistor. It was found that an input voltage of -5V, a voltage side resistor of 2.5k $\Omega$ , and a ground side resistor of 100 $\Omega$  produced the required output voltage of -0.192V.

Once the triangle waveform had been sufficiently modified by the circuitry to meet the FSCV parameters for dopamine oxidization and reduction, the signal could be sent to the working electrode, where the reference electrode could pick up the resulting fluctuations in the current present in the sample. The resulting signal was then passed through a current-to-voltage converter and amplifier circuit shown in Figure 4. This circuitry was left largely unchanged from the previous work completed by Jayson Foster at GVSU.

Figure 4. Current-to-Voltage Converter and Amplifier Circuit

The current follower equation shown below would then allow the current at the reference electrode to be calculated.

$$V_{out} = -iR_f \tag{2}$$

Where  $V_{out}$  is the output voltage of the current-to-voltage converter, *i* is the current at the reference electrode, and  $R_f$  is the feedback resistor. For this project a feedback resistor of  $10k\Omega$  was used. The signal next needed to pass through the amplifier portion of the circuit so that the very small signal could be read by the board. This part of the circuit is governed by equation 3:

$$V_{out} = -V_{in} \frac{R_f}{R_i} \tag{3}$$

Where  $V_{out}$  is the output voltage of the amplifier,  $V_{in}$  is the input voltage,  $R_f$  is the feedback resistor, and  $R_i$  is the input resistor. For this portion of the circuit a feedback resistor of  $10k\Omega$ and an input resistor of  $560\Omega$  were used. This signal was then passed back to the Hercules board to be measured by the onboard ADC.

#### Software

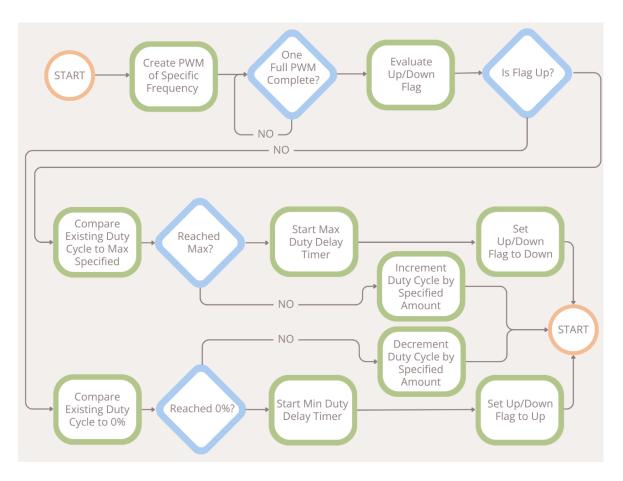

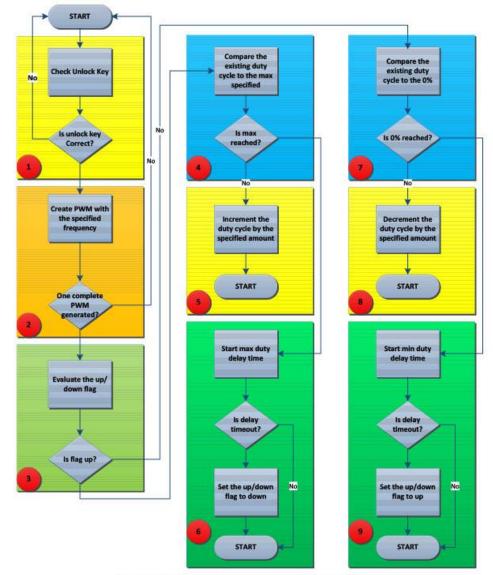

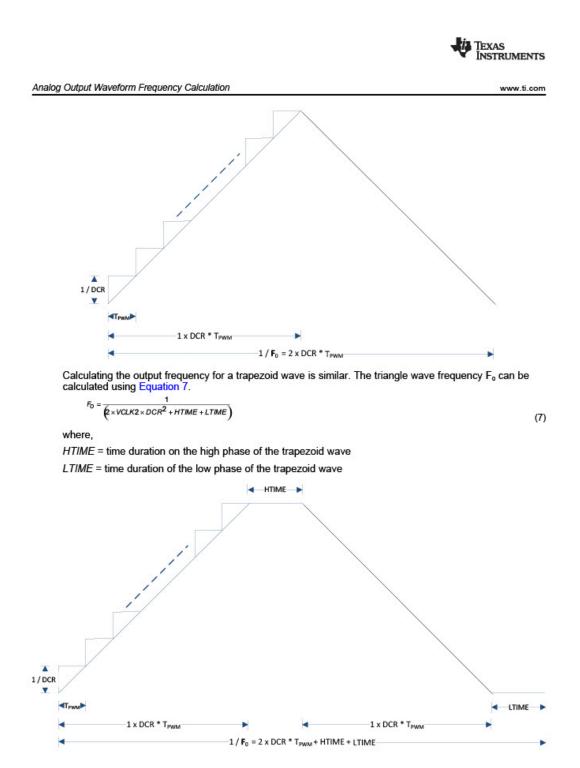

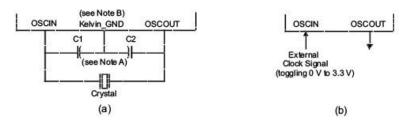

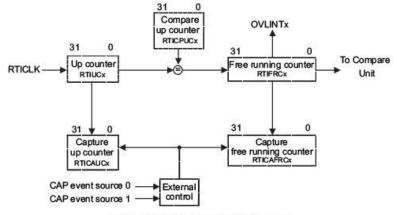

The first software step for this project was the development of the code to produce the PWM signal for the custom triangle waveform required for the oxidation and reduction reactions. The block diagram for this code is shown below in Figure 5.

Figure 5. Block Diagram for PWM Triangle Wave Generation Code

The implementation is as follows:

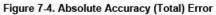

- The specified PWM is generated starting with 0% duty cycle. The duty cycle will be selfmodified by the N2HET1. Wait until one full PWM period is generated before changing to a new duty cycle.

- 2. The up/down flag is evaluated to determine whether the duty cycle should increase or decrease. The flag will be initialized to zero after reset, meaning to increment the duty cycle, thus increasing the resulting PWM voltage. If the flag is 1, the duty cycle will decrement instead, thus decreasing the resulting PWM voltage.

- 3. The existing duty cycle is compared to the programmed maximum duty cycle. This parameter determines the maximum voltage the PWM signal will reach. The maximum

duty cycle is a parameter changeable by the host CPU before the N2HET program starts. If the maximum is reached, go to step 5.

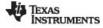

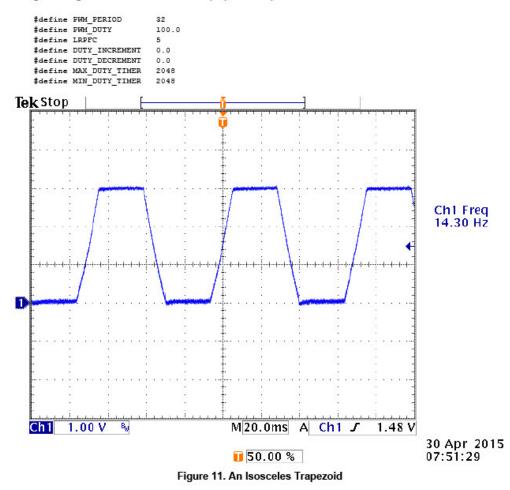

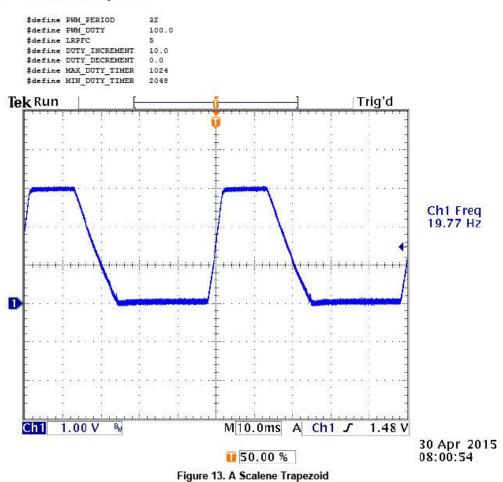

- 4. The next duty cycle percentage is incremented by the programmed amount. This parameter determines the slope of the incline of the PWM wave.

- 5. A programmed timer is started. The timer is used to hold the PWM at the maximum duty cycle for a programmable amount of time. This step would be needed for creating trapezoid waveforms. In the present case, since a triangle wave is required, this timer delay was set to zero.

- 6. The existing duty cycle is compared to the 0% duty cycle. If 0% is reached, go to step 8.

- 7. The next duty cycle is decremented by the programmed amount. This parameter determines the slope of the decline of the PWM wave. Note that the amount to decrement can be different than the amount to increment to generate a sawtooth; however, this was not required in the present work.

- 8. A programmed timer is started. The timer is used to hold the PWM at the 0% duty cycle for a programmable amount of time. Note that this minimum duty cycle timer length can be different from the maximum duty cycle timer length. This was used to implement the time delay between individual triangle waves.

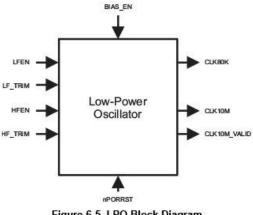

In order to implement the HET code, the N2HET Assembler from TI was used. The assembler translates the higher-level HET code, which can be found in Appendix II, so that it could be used by the HALCoGen software from TI to generate all the needed c and header files for the project. HALCoGen stands for Hardware Abstraction Layer Code Generator. Once HALCoGen had generated the project it was opened in Code Composer Studio where the main.c file could be written. This file was also pre-generated by HALCoGen with a skeleton code

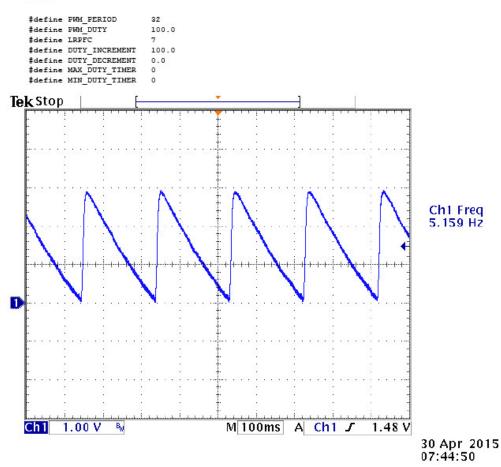

consisting mainly of comments outlining where various parts of the code should be written so the file can remain interpretable by the HALCoGen tool. The code added to the main.c file includes 8 configurable macros which control the parameters of the triangle wave to be produced. They are: LRPFC, PWM\_PERIOD, PWM\_DUTY, DUTY\_INCREMENT, DUTY\_DECREMENT, MAX\_DUTY\_TIMER, MIN\_DUTY\_TIMER, and NHET1\_PIN\_PWM.

The carrier frequency of the PWM signal can be expressed in terms of the Loop Resolution Period (LRP). This is the frequency at which the HET module will loop through the HET code.

$$LRP = VCLK2 \times 2^{LRPFC} \times PWM\_PERIOD$$

(4)

In the equation shown above the VCLK2 is the clock speed which equals 11.11ns. LRPFC is the first configurable macro and stands for Loop Resolution Pre-scaler Factor Coefficient. The possible values for this macro are 5, 6, or 7. PWM\_PERIOD is the second configurable macro and can be set to an integer in the range of 1 to 32. So if, for instance, LRPFC is set to 6 and PWM\_PERIOD is set to 1, the NHET has 64 clock cycles for 1 LRP. This means the NHET can modulate the duty cycle between these 64 steps, giving a 6-bit resolution for the amplitude of the output signal. This resolution can be improved by increasing either LRPFC or PWM\_PERIOD. For example, with and LRPFC set to 7 and PWM\_PERIOD set to 32, 1 LRP is equivalent to 4096 clock cycles giving a 12-bit resolution. The higher the resolution the less noise present in the final analog signal. However, this comes with a tradeoff; the higher the resolution, the lower the possible output frequency that can be generated. If a higher frequency output signal is required, some resolution would have to be sacrificed. For the purposes of this project LRPFC

was set to 6 and PWM\_PERIOD was set to 32 giving an LRP of 2048 clock cycles or an 11-bit resolution.

The next configurable macro is PWM\_DUTY, which represents the maximum duty cycle the NHET will be allowed to reach. Practically speaking this is the max amplitude of the filtered output signal. This variable is expressed as a percentage of the total possible duty cycle and has a possible range of 0.1% to 100% which would allow the output signal to have a max amplitude anywhere in the range of 0.33mV to 3.3V.

DUTY\_INCREMENT and DUTY\_DECREMENT are the next configurable macros, and they represent the amount to increase or decrease the duty cycle from one step to the next. This variable is also given as a percentage in the range 0.1% to 100%. In the output signal these control the slope of the rise and the fall. These two macros can be set to different values to generate a sawtooth wave if that is required. The present work required a triangle wave so they were both set to the same value.

MAX\_DUTY\_TIMER and MIN\_DUTY\_TIMER represent the amount of time for which the system will maintain either the maximum or minimum duty cycle and is expressed in terms of number of LRP. This is used to change the amount of time the output signal will hold at either the maximum or minimum value and is thus useful for generating a trapezoid wave. The signal produced in this project is a triangle pulse with a delay between each during which the signal remains at baseline. In order to accomplish this, the MAX\_DUTY\_TIMER was set to 0 and the MIN\_DUTY\_TIMER was set to around 4000 LRP which produced a delay of around 90ms.

The final macro is NHET1\_PIN\_PWM which defines the pin number at which the PWM signal will be produced. For this project, PIN\_HET\_0 was used.

28

The next software to be written was the code to read the signal coming into the ADC for measurement. All the necessary include files for this portion of the code were also generated with the HALCoGen tool. These included the files for utilizing both the ADC module to read the voltage at the input pin, as well as the SCI module to print the values in a terminal window on the PC. Additional code was added to the main.c file to implement both of these tasks. The key pieces of code for this part of the main function are shown below in Figure 6. The full main.c file with all of these parameters and functions can be found in Appendix II.

```

adcData_t adc_data; //ADC data structure

adcData_t *adc_data_ptr = &adc_data; //ADC data pointer

unsigned int NumberOfChars, value; //Declare variables

sciInit(); //Initializes the SCI (UART) module

adcInit(); //Initializes the ADC module

while(1)

{

adcStartConversion(adcREG1, adcGROUP1); //Start ADC conversion

while(!adcIsConversionComplete(adcREG1, adcGROUP1)); //Wait for ADC conversion

adcGetData(adcREG1, 10, adc_data_ptr); //Store conversion into ADC pointer

value = (unsigned_int)adc_data_ptr->value;

NumberOfChars = ltoa(value, (char*)command);

sciSend(sci1inREG, 2, (unsigned char *)"0x"); //Sends hex designation

sciSend(sci1inREG, 2, (unsigned char *)"\r\n"); //Sends new line character

}

```

Figure 6. Main Function Code for ADC and SCI Modules

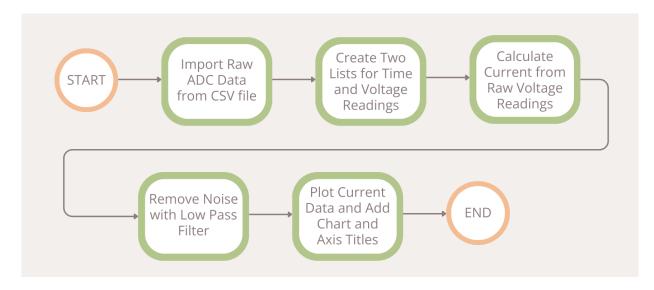

The final software step in this project was the development of a python script to process the raw data from the board and make the necessary calculations to visualize the current change in the sample. This script utilized both equations 2 and 3 to perform these calculations and then used a basic digital lowpass Butterworth filter to remove the noise. The simple block diagram for this script is shown below in Figure 7.

Figure 7. Block Diagram for Data Processing Python Script

# **Chapter 4 Results**

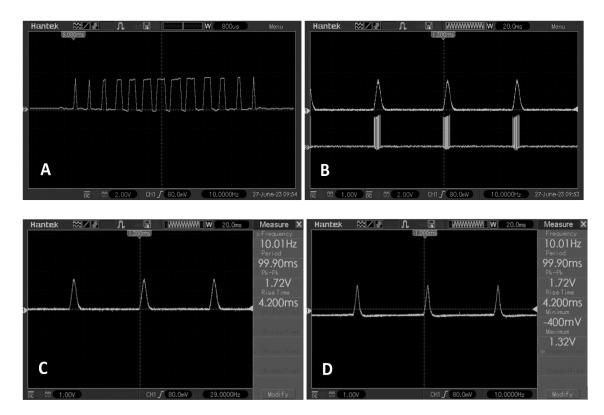

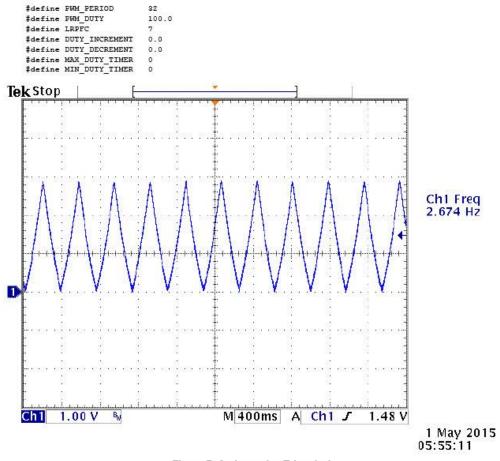

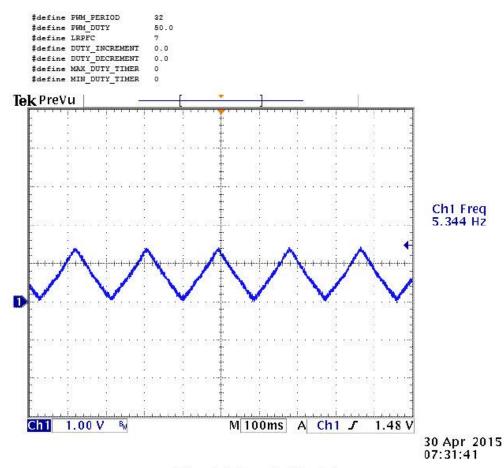

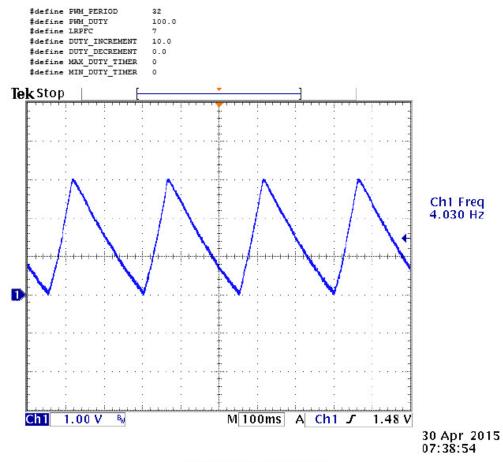

The PWM output from the board as well as the resulting waveforms after both the initial analog lowpass filter as well as the voltage divider were visualized using an oscilloscope. These can be found below in Figure 8. Measurement A in Figure 8 shows a single, raw PWM signal coming from the Hercules board. This makes it possible to visualize the duty cycle increasing and then decreasing. Measurement B in Figure 8 shows three PWM signals both before (bottom) and after (top) the analog low pass filter. The low pass filter produced a triangle wave from the variable duty-cycle PWM signal. Measurement C in Figure 8 shows that the triangle wave, after the low pass filter, has a period of 99.9ms, a peak-to-peak voltage of 1.72V, and a rise time of 4.2ms. Measurement D in Figure 8 shows the triangle wave after the voltage divider biasing circuit has the same period, peak-to-peak voltage, and rise time as that of Measurement C but now with a minimum voltage of -0.4V and a maximum voltage of 1.32V.

Figure 8. Oscilloscope Measurements of Triangle Wave Generation

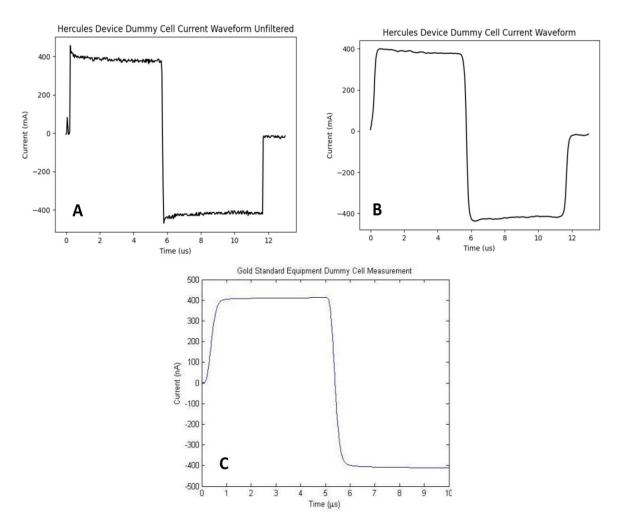

In place of a dopamine solution, a dummy cell constructed from a 1nF capacitor and a  $100k\Omega$  resistor was used to test the device. Figure 9 below shows the dummy cell current waveform measurement taken with the present device both before and after the filtering done within the algorithm, compared to the same measurement made with the gold standard equipment. Chart A in Figure 9 shows the measurement taken with the Hercules device without the digital Butterworth filter applied, chart B in Figure 9 shows the measurement taken with the Hercules device 9 shows the measurement taken with the measurement taken with the digital Butterworth filter applied, and chart C in Figure 9 shows the measurement taken with the gold standard equipment.

Figure 9. Current Waveform Outputs for Dummy Cell, (A) Hercules Device Unfiltered, (B)

Hercules Device with Butterworth Filter, (C) Gold Standard [20]

All three measurements show the current steeply increasing from 0 to around 400nA, holding there for around 6µs, steeply decreasing to -400nA, and holding there for around 6µs. The measurement from the gold standard equipment held very steady at both the high and low ends, whereas the Hercules device was quite noisy in these areas. A digital lowpass Butterworth filter was used to combat some of this noise.

The price of all the components that were purchased to construct the device was tabulated so that the total cost could be calculated. The bill of materials can be found below in Table 1. The total cost to develop the device came to \$108.

| Item                     | Cost  |

|--------------------------|-------|

| Hercules Development Kit | \$50  |

| Basic Electronics Kit    | \$15  |

| Resistors Kit            | \$10  |

| Op Amp Kit               | \$15  |

| Capacitor Kit            | \$13  |

| DC-DC Pos+Neg ±5V Reg    | \$5   |

| Total                    | \$108 |

Table 1. Project Bill of Materials

For the sake of discussion, the cost of just the individual components used rather than the full cost of the electronics kits that were purchased for the development of the circuit was also

tabulated. This information can be found below in Table 2. The total cost to build the device as described in this paper is \$61.29.

| Item                           | Cost    |

|--------------------------------|---------|

| Hercules Development Kit       | \$50    |

| LM2902n Op Amp                 | \$0.43  |

| 10kΩ Resistor (X3)             | \$0.30  |

| 560 $\Omega$ Resistor          | \$0.10  |

| 220 $\Omega$ Resistor          | \$0.10  |

| 100 $\Omega$ Resistor          | \$0.10  |

| $2.5 \text{ k}\Omega$ Resistor | \$0.64  |

| 2.2 nF ceramic Capacitor       | \$2.25  |

| 3 10 uF capacitor              | \$2.37  |

| DC-DC Pos+Neg ±5V Reg          | \$5     |

| Total                          | \$61.29 |

Table 2. Component Only Bill of Materials

## **Chapter 5 Discussion and Conclusion**

## Discussion

The Triangle wave produced met all the required parameters for FSCV. These parameters are: a period of 100ms, a rise time of 4.2ms, a resting voltage of -0.4V, and a peak voltage of 1.3V. The PWM signal produced by the board met the first two of these parameters once it was passed through the analog low pass filter. The voltage divider biasing circuit was then able to successfully shift the signal down to a resting voltage of -0.4V in order to achieve the final two parameters. The peak voltage this device was able to achieve was 1.32V, which varies just slightly from the ideal parameter. This 20mV error is likely due to simplicity of the circuitry and the nature of filtering a PWM signal into a triangle wave. Because FSCV of dopamine simply requires that dopamine's oxidation voltage of 0.6V and subsequently, its reduction voltage of -0.1V be reached within a certain timing, the maximum value is less critical and therefore the 20mV difference is acceptable. The key advantage of utilizing PWM to generate the triangle waveform as opposed to a DAC as seen in previous work is that the process requires nothing from the main CPU once the NHET is configured leaving all available processing power available for data collection and transmission to the PC. In addition, the PWM signal generation method remains highly configurable allowing for the possibility of configuring different triangle waves with ease within the code. A key disadvantage however is that due to the nature of variable duty cycle PWM there is an inherent tradeoff between noise and frequency: the higher the resolution (lower noise) the lower the possible output frequency. This disadvantage is acceptable given that the goal of the system isn't to achieve a perfect, noiseless signal, but to produce a passable signal at a low cost.

The Python script accurately calculated the current based on the data collected by the onboard analog to digital converter. The dummy cell measurement taken with the device matches the characteristic waveform seen with the gold standard equipment. This indicates that the device is capable of performing Fast Scan Cyclic Voltammetry for dopamine solutions. The discrepancies between the measurements taken with the Hercules device and the measurements taken with the gold standard equipment were to be expected. The simple, low cost, DIY nature of this project meant the resulting measurements would be noisier and less accurate than those taken on very expensive equipment. There are a couple of likely sources of this noise. The first is inherent noise within the ADC on the launchpad. This is likely a minor contributor to the noise. Another potential source would be noise introduced into the signal during waveform generation. It is the nature of PWM as a very high frequency signal of variable duty cycle which is then filtered into a much lower frequency signal to retain some of that high frequency component after the filtering process. The method utilized in the present work to mitigate the noise was the use of a digital lowpass Butterworth filter during the signal processing phase, but an analog lowpass filter prior to data collection by the ADC may also have been an effective noise reduction method to explore. All that said, this tradeoff between the quality of the measurement and the cost to perform the measurement is acceptable, provided that the information able to be obtained with the Hercules device is still accurate *enough* to give researchers an indication of what more expensive measurement techniques may reveal. Given the similarity between the measurements taken with both the gold standard equipment and the present device, it's safe to say these measurements are indeed accurate enough.

The Device consists of just one microcontroller with total bill of materials for development coming in well under budget at \$108. This means the project achieved the

36

objectives to simplify the device put forth by Jayson Foster, GVSU and to keep the device under \$200. Additionally, if the device were to be built as specified in this paper, the need for the hardware 'kits' that were purchased would be eliminated and the total cost would be just \$61.29.

## Conclusion

All of the objectives of this project were achieved. The device was able to successfully produce the required waveform and collect the results. This project offers proof of concept for the use of PWM in the generation of a FSCV triangle waveform for dopamine concentration measurement. By utilizing a PWM signal generated with a module independent from the main CPU to produce the triangle wave, the need for two microcontrollers, as seen in previous work, was eliminated, thus simplifying the device. All of the materials used in this project are readily available from online retailers, making this device highly accessible. The final cost to construct the device came to \$108 making the project highly affordable.

### **Future Work**

Due to COVID closures and personal constraints, it was not possible to test the system in a lab setting with dopamine solutions. A critical next step for this work would be to verify its effectiveness in lab use. Additionally, the current process requires the user to take the output from the microcontroller and manually run it through the python script in order to generate the output. An important next step would require the development of an app that's capable of initiating the microcontroller, starting a cycle, and then automatically processing the data with the python algorithm. This would greatly improve the usability of the device. Finally, with further development, the device could be made compatible with a variety of electrode configurations and be made capable of producing multiple waveforms to allow the measurement of different neurotransmitters, such as serotonin, thus making the device more flexible.

37

# Appendices

# **Appendix I – Schematic**

### **Appendix II – Hercules Microcontroller Code**

### **High Level HET code**

;;;;;; ; This example code is to be loaded into N2HET1's RAM. This code will generate a ; time-varying PWM signal to render either triangle waves or trapezoid waves. ;;;;;; ; PWM frequency to be generated PWM\_PERIOD .equ 2 ; The pin number that will output the PWM signal PWM PIN NUM .equ 9 ; The initial maximum duty cycle (LR compare value) to be generated. INIT COMPARE .equ 3 ; The initial maximum duty cycle (HR compare value) to be generated. INIT COMPARE HR .equ 0 ; amount of increment in terms of LRP. Note the total amount to increment is ; equal to DUTY\_INCREMENT + DUTY\_INCREMENT\_HR. DUTY INCREMEMT .equ 0 ; amount of increment in terms of HR. DUTY\_INCREMEMT\_HR .equ 1 ; amount of decrement in terms of LRP DUTY\_DECREMEMT .equ 0 ; amount of decrement in terms of HR DUTY DECREMEMT HR .equ 1 ; amount of timer delay to keep the PWM at 0% duty cycle LOW DELAY .equ 0 ; amount of timer delay to keep the PWM at maximum duty cycle HIGH DELAY .equ 0 ; key to unlock N2HET UNLOCK\_KEY .equ 0xA ; The data field of the MOV32 instruction contains an initial value (0x5) that ; is not equal to the key to unlock the N2HET program. First the MOV32 ; instruction moves the initial value to a temporary register T L00 MOV32 { remote=DUMMY,type=IMTOREG,reg=T,data=0x5}; ; Compare the register T value with the key to unlock N2HET. The key to unlock ; is 0xA. If the key is not matched then go back to L00. The CPU is supposed ; to write the proper key (0xA) to unlock the N2HET L01 ECMP { next=L00,hr\_lr=L0W,cond\_addr=L02,pin=0,reg=T,data=UNLOCK\_KEY}; ; Creating a virtual counter using CNT which will determine the period of ; the PWM to be generated. The initial small max count allows for quick ; simulation which can later be changed by the host CPU. L02 CNT { reg=A, irq=OFF, max=PWM PERIOD}; ; Use ECMP to determine the duty cycle of the PWM on the specified pin. The ; pin field and the duty cycle are changeable by the CPU. L03 ECMP { hr lr=HIGH,en pin action=ON,cond addr=L04,pin=PWM PIN NUM, action=PULSELO,reg=A,irq=OFF,data=0,hr data=0}; ; Only when the CNT reaches the max count will the program go to the : conditional address. We want to wait for one complete PWM waveform to be ; generated before changing the duty cycle. When CNT reaches the max ; value it will set the Z flag.

```

L04 BR { next=L00,cond_addr=L05,event=Z};

; the data field in this ADD acts as a up/down flag. To create either a triangle

; or a trapezoid wave we first need to create a ramp up waveform. The PWM will first

; increase the duty cycle until it reaches the specified maximum duty cycle before

; it starts to decrease the duty or stay at the maximum duty. The up/down flag is

; used to create two different paths in the flow to alternate before increasing duty

; cycle vs decreasing duty cycle.

L05 ADD { src1=ZERO, src2=ZERO, dest=NONE, data=0};

; Move the up/down flag to a temp register T.

L06 MOV32 { remote=L05,type=REMTOREG,reg=T};

; Compare this up/down flag to 0. 0 means to increase the duty cycle and 1

; means to decrease the duty cycle.

L07 ECMP { next=L16,cond addr=L08,pin=0,reg=T,data=0};

; move the ECMP DF which contains the compare value for duty cycle creation

; to register R

L08 MOV32 { remote=L03,type=REMTOREG,reg=R};

; Subtract the current compare value from the max duty cycle stored in

; REM DUTY. The result will be stored in register S.

L09 SUB { src1=REM, src2=R, dest=S, remote=REM DUTY, data=0};

; If the subtraction result is more than 0 then it means it has not

; reached the max duty cycle we will increase the duty cycle. If it is

; zero or less than zero then we have reached the max duty cycle and we

; will change the up/down flag to down position.

L10 BR { next=L12, cond addr=L11, event=GT};

; Add specified amount to the existing compare value (duty cycle) to specify the new

; duty cycle. The amount to increment is changeable by CPU before the N2HET program

starts.

; After the addition, jump back to the beginning of the program

L11 ADD { next=L15,src1=R,src2=IMM,dest=S,rdest=REM,remote=L03,data=DUTY INCREMEMT,

hr_data=DUTY_INCREMEMT_HR};

; Insert a timer delay after the maximum duty cycle is reached. A timer delay here

has the

; effect of creating the high side of a trapezoid waveform. If the timer is zero then

it

; becomes a triangle wave.

L12 DJZ { next=L00,cond_addr=L13,reg=NONE,data=HIGH_DELAY};

; After the above DJZ expires on its counter we need to reload the DJZ counter to the

; specified amount of delay.

L13 MOV32 { next=L14, remote=L12, type=IMTOREG&REM, reg=NONE, data=HIGH DELAY};

; Now change the up/down flag to down by moving a 1 to the up/down flag

L14 MOV32 { remote=L05,type=IMTOREG&REM,reg=NONE,data=1};

; Branch to the beginning

L15 BR { next=L00,cond addr=L00,event=NOCOND};

; move the ECMP DF to register R which contains the current compare value

; (duty cycle)

L16 MOV32 { remote=L03,type=REMTOREG,reg=R};

; Subtract the current duty cycle by the specified amount. This amount of decrement

is

; changeable by CPU before the N2HET program starts. When this instruction is

executed

; the first time, the current duty cycle is at the maximum duty cycle. Here we are

creating

; the ramp down part of the triangle/trapezoid waveforms.

```

L17 SUB { src1=R, src2=IMM, dest=S, rdest=NONE, data=DUTY\_DECREMEMT,

### hr\_data=DUTY\_DECREMEMT\_HR};

; As long as the subtraction result is greater than zero, we will keep ; decreasing the duty cyle or otherwise we will again change the up/down ; flag to up position. The destination register is S which contains the ; subtraction result. L18 BR { next=L19, cond addr=L20, event=N}; ; Move the subtraction result to the ECMP DF as the new duty cycle L19 MOV32 { next=L00,remote=L03,type=REGTOREM,reg=S}; ; Insert a timer delay after the 0% duty cycle is reached. A timer delay here has the ; effect of creating the low side of a trapezoid waveform. If the timer is zero then it ; becomes a triangle wave. L20 DJZ { next=L00,cond addr=L21,reg=NONE,data=LOW DELAY}; ; Reset the increment delay to the specified amount. L21 MOV32 {remote=L20,type=IMTOREG&REM,reg=NONE,data=LOW DELAY}; ; Move the value 0 to the up/down flag so in the next LRP the program ; flow will execute the path to increase duty cycle. L22 MOV32 { remote=L05,type=IMTOREG&REM,reg=NONE,data=0}; ; Branch to beginning L23 BR { next=L00,cond addr=L00,event=NOCOND}; ; REM\_DUTY data field stores the maximum duty cycle the PWM to be generated. ; The host CPU can change this value. REM DUTY ECMP { next=REM DUTY,cond addr=REM DUTY,pin=0,reg=A,data=INIT COMPARE, hr\_data=INIT\_COMPARE\_HR};

```

DUMMY BR { next=DUMMY,cond_addr=DUMMY,event=NOCOND,irq=OFF};

```

### main.c

```

/** @file sys main.c

*

@brief Application main file

*

@date 16.Feb.2015

*

@version 04.03.00

*

*

This file contains an empty main function,

*

which can be used for the application.

*/

* Copyright (C) 2009-2015 Texas Instruments Incorporated - www.ti.com

*

*

Redistribution and use in source and binary forms, with or without

modification, are permitted provided that the following conditions

*

are met:

*

*

Redistributions of source code must retain the above copyright

*

notice, this list of conditions and the following disclaimer.

```

\* \* Redistributions in binary form must reproduce the above copyright \* notice, this list of conditions and the following disclaimer in the \* documentation and/or other materials provided with the distribution. \* \* Neither the name of Texas Instruments Incorporated nor the names of \* its contributors may be used to endorse or promote products derived \* from this software without specific prior written permission. \* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT \* LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR \* \* A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT \* OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, \* SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT \* LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, \* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY \* THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT \* (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE \* OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. \* \*/

/\* USER CODE BEGIN (0) \*/